1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

| module mul_cell

#(parameter N=4,

parameter M=4

)(

input clk,

input rstn,

input en,

input[M+N-1:0] mult1,

input[M-1:0] mult2,

input[M+N-1:0] mult1_acci,

output reg[M+N-1:0] mult1_o,

output reg[M-1:0] mult2_shift,

output reg[N+M-1:0] mult1_acco,

output reg rdy

);

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

rdy <= 'b0 ;

mult1_o <= 'b0 ;

mult1_acco <= 'b0 ;

mult2_shift <= 'b0 ;

end

else if (en) begin

rdy <= 1'b1 ;

mult2_shift <= mult2 >> 1 ;

mult1_o <= mult1 << 1 ;

if (mult2[0]) begin

mult1_acco <= mult1_acci + mult1 ;

end

else begin

mult1_acco <= mult1_acci ;

end

end

else begin

rdy <= 'b0 ;

mult1_o <= 'b0 ;

mult1_acco <= 'b0 ;

mult2_shift <= 'b0 ;

end

end

endmodule

module mul_main

#(parameter N=4,

parameter M=4

)(

input clk,

input rstn,

input data_rdy ,

input[N-1:0] mult1,

input[M-1:0] mult2,

output res_rdy,

output[N+M-1:0] res

);

wire [N+M-1:0] mult1_t [M-1:0] ;

wire [M-1:0] mult2_t [M-1:0] ;

wire [N+M-1:0] mult1_acc_t [M-1:0] ;

wire [M-1:0] rdy_t ;

mul_cell #(

.N(N),

.M(M)

)

u_mult_step0(

.clk (clk),

.rstn (rstn),

.en (data_rdy),

.mult1 ({{(M){1'b0}}, mult1}),

.mult2 (mult2),

.mult1_acci ({(N+M){1'b0}}),

.mult1_acco (mult1_acc_t[0]),

.mult2_shift (mult2_t[0]),

.mult1_o (mult1_t[0]),

.rdy (rdy_t[0])

);

genvar i;

generate

for(i=1; i<=M-1; i=i+1) begin

mul_cell #(

.N(N),

.M(M)

)

u_mult_step(

.clk(clk),

.rstn(rstn),

.en(rdy_t[i-1]),

.mult1(mult1_t[i-1]),

.mult2(mult2_t[i-1]),

.mult1_acci(mult1_acc_t[i-1]),

.mult1_acco(mult1_acc_t[i]),

.mult1_o(mult1_t[i]),

.mult2_shift(mult2_t[i]),

.rdy(rdy_t[i])

);

end

endgenerate

assign res_rdy = rdy_t[M-1];

assign res = mult1_acc_t[M-1];

endmodule

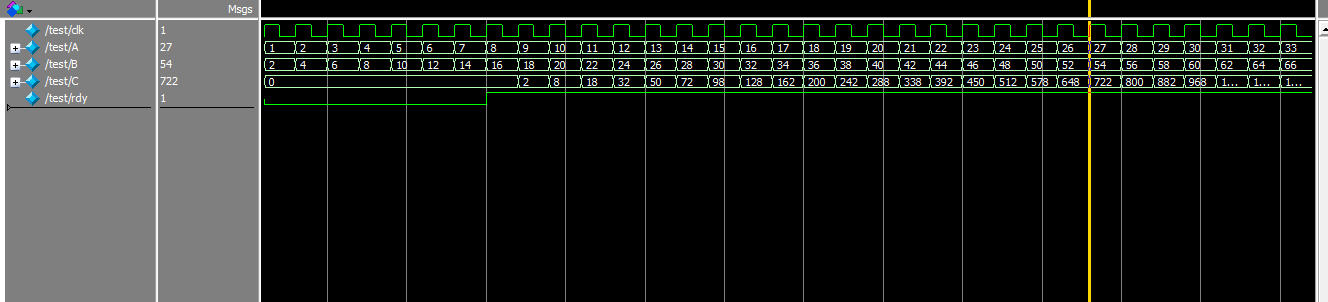

`timescale 1ps/1ps

module test ();

reg clk=0;

reg[7:0] A=0;

reg[7:0] B=0;

always begin

#1 clk = ~clk;

end

always @(posedge clk) begin

A = A + 1;

B = B + 2;

end

wire[15:0] C;

wire rdy;

mul_main #(

.N(8),

.M(8)

)

mul(

.clk(clk),

.rstn(1'b1),

.data_rdy(1'b1),

.mult1(A),

.mult2(B),

.res_rdy(rdy),

.res(C)

);

endmodule

|